Proceedings of the 2<sup>nd</sup> International Conference of Theoretical and Applied Nanoscience and Nanotechnology (TANN'18) Niagara Falls, Canada – June 10 – 12, 2018 Paper No. 135 DOI: 10.11159/tann18.135

# Electrical Characteristics of Cylindrical Gate-All-Around CGAA Tunnel FET<sub>s</sub>

## Mohamed Kessi<sup>1</sup>, Lounas Belhimer<sup>2</sup>

Faculty of Electrical Engineering and Computer Sciences, University M. Mammeri, Tizi-Ouzou, UMMTO DZ 15000, Algeria kessi\_mohamed@hotmail.com; lounasbelhimer@yahoo.fr

**Abstract** - Recently, the Cylindrical Gate-all-Around CGAA MOSFET is considered as the promising device structure and a vital element for Vertical CMOS technology. However device optimization is still under investigations. In this work, electrical characteristics of Cylindrical GAA (CGAA) MOSFET are systematically analyzed. We evaluated and studied the length dependence of ON current ( $I_{ON}$ ), and subthreshold leakage current ( $I_{OF}$ ) with different device parameters, especially channel length (Lg), channel thickness ( $t_{si}$ ), oxide thickness ( $t_{ox}$ ), and gate work function ( $\Phi_M$ ), using the finite element, numerical method by solving Poisson's equation in Cylindrical coordinate system.

*Keywords:* Cylindrical Gate-all-Around CGAA, MOSFET, Subthreshold leakage current (I<sub>OF</sub>), ON current (I<sub>ON</sub>), Short Channel Effects (SCEs).

#### 1. Introduction

The research community of microelectronics are subjected to have large computing power with less power conception and smaller dimensions has lead to nano dimension of device miniaturization in order to maximize integration in integrated circuit ( $IC_s$ ) as possible to increase its efficiency.

The down-scaling of conventional MOSFETs has led to an impending power crisis, in which static power consumption is becoming too high. In order to improve the energy-efficiency of electronic circuits, small swing switches are interesting candidates to replace or complement the MOSFETs used today.

Complementary metal-oxide-semiconductor (CMOS) technology has led to the steady minimization of transistors with each new generation, thereby yielding continuous improvements in transistor performance.

However, the International Technology Roadmap for Semiconductors (ITRS) had indicated that the scaling of gate transistor lengths to sub-22 nm levels could yield several serious problems, such as high sub-threshold leakages, short-channel effects, device-to device variations [1].

Several various designs structures has been developed, including: double-gate, tri-gate,  $\Omega$ -gate,  $\Pi$ -gate and gate-allaround (GAA), all make use of enhanced gate control due to the action of multiple electrodes surrounding the channel [2]-[3].

Also the electrical characteristics of a new structure CGAA has investigated indeed the effect of physical and geometrical parameters like channel length (Lg), channel thickness ( $t_{Si}$ ), oxide thickness ( $t_{OX}$ ) and gate work function ( $\phi_M$ ) as, are very much sensitive to the device performance like threshold voltage ( $V_{th}$ ), and On-Off ration ( $I_{ON}/I_{OF}$ ).

#### 2. Device Structure and Parameters

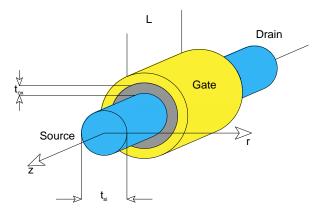

The schematic diagram of the Cylindrical GAA (CGAA) MOSFET structures used for simulation is shown in Fig. 1. The details of device physical parameters used in the structure are shown in Table 1.

Fig. 1: Schematic structure of Cylindrical Gate-All-Around (GAA) MOSFET<sub>s</sub>.

| symbol          | Parameter                               | Value                    |

|-----------------|-----------------------------------------|--------------------------|

| Na              | Impurity doping in the channel          | $10^{16} \text{cm}^{-3}$ |

| N <sub>d</sub>  | Impurity doping in the source and drain | $10^{20} \text{cm}^{-3}$ |

| R               | Channel radius                          | 5nm                      |

| t <sub>si</sub> | Silicon film thickness                  | 10nm                     |

| $L_S, L_D$      | Length of source and drain              | 5nm                      |

| t <sub>ox</sub> | Oxide thickness                         | 1nm                      |

| L               | Channel length                          | 30nm                     |

| ε <sub>0</sub>  | Permittivity of vacuum                  | 8.8*10 <sup>12</sup> F/m |

| ε <sub>si</sub> | Permittivity of silicon                 | 11.85* ε <sub>0</sub>    |

| ε <sub>ox</sub> | Permittivity of oxide                   | 3.9* ε <sub>0</sub>      |

| Т               | Absolute temperature in Kelvin          | 300K                     |

| $\Phi_{\rm M}$  | Metal work function                     | 4.6eV                    |

Table 1: Values of various parameters used in simulation.

#### 3. Results and Discussion

In order to analyze the impact of channel length (*Lg*), and channel thickness (tsi), and gate work function ( $\phi_M$ ), on the device performance, the simulation is carried out by varying the above parameters.

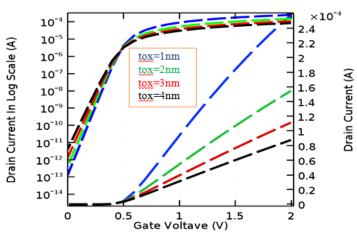

Fig. 2: Drain current  $(I_D)$  in log and linear scale as a function of gate to source voltage  $(V_{GS})$  at different oxide thickness at  $V_{DS}$ =50 mV.

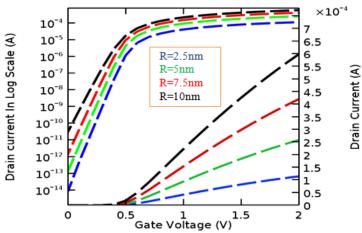

Fig. 3: Drain current ( $I_D$ ) in log scale as a function of gate to source voltage ( $V_{GS}$ ) at different silicon body thickness (tsi)at  $V_{DS}$ =50 mV.

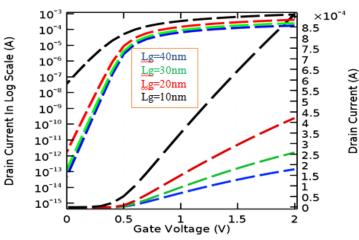

Fig. 4: Drain current ( $I_D$ ) in log scale as a function of gate to source voltage ( $V_{GS}$ ) at different channel length at  $V_{DS}$ =50 mV.

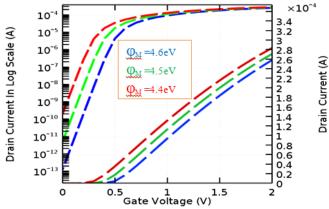

Fig. 5 Drain current ( $I_D$ ) in log scale as a function of gate to source voltage ( $V_{GS}$ ) at different gate work function at  $V_{DS}$ =50 mV.

Fig.2 represents  $I_D$ - $V_{GS}$  characteristics for CGAA MOSFET at different oxide thicknes. We can conclude for this variation that thinner gate oxides lead to product higher drain currents. And if increase oxide thickness the threshold voltage decrease.

Fig.3 illustrates characteristics for CGAA MOSFET<sub>s</sub> at various of silicon body thickness (tsi). We can observe that if the channel length decreases reduce the current and the characteristics of  $I_{off}$  is also influenced by (tsi). As the channel thickness gets thinner, there is a significant improvement in leakage current.

In Fig. 4 show the drain current  $(I_D)$  as a function of the gate to source voltage  $(V_{GS})$  for different channel length. We can analyze from the figures that when in reduce Lg the drain current augment and the threshold voltage  $(V_{th})$  reduce.

Fig.5 reveals the drain current (I<sub>D</sub>) dependency on different values of metal gate work function ( $\phi_M$ ). The results illustrate that the subthreshold performance (off-state leakage current) of the device improves for higher values of metal gate work function. Higher the  $\phi_M$  increases threshold voltage that reduces leakage current and improves the subthreshold behavior of the device.

### 4. Conclution

In this paper, we have proposed the length sensitivity dependence of ON current ( $I_{ON}$ ), subthreshold leakage current ( $I_{OF}$ ) and the threshold voltage ( $V_{TH}$ ). The variations of individual parameters of the structure were performed to calculate their effect on the characteristics of the device. The simulation has been found that the CGAA MOSFET<sub>S</sub> has very good SCE immunity and improvement in the device reliability. Other characteristics have been studied but not included in this paper.

#### References

- [1] F. Assad, Z. Ren, D. Vasileska et al., "On the Performance Limits for Si MOSFET's: A Theoretical Study," *IEEE Transactions On Electron Devices*, vol. 47, no. 1, pp. 232-40, 2000.

- [2] V. M. Srivastava, K. S. Yadav, and G. Singh, "Design and performance analysis of double-gate MOSFET over single-gate MOSFET for RF switch," *Microelectronics J.*, vol. 42, no. 3, pp. 527-534, 2011.

- [3] P. Colinge, "Multi-gate SOI MOSFETs," *Microelectronic Engineering*, vol. 84, no. 9-10, pp. 2071-2076, 2007.